# **SYSTEM 2400**

# SOFTWARE

# MACHINE CODE AND ASSEMBLY LANGUAGE

MOHAWK DATA SCIENCES CORP.

# SYSTEM 2400

# MACHINE CODE AND ASSEMBLY LANGUAGE

(Level 03, Revision 03 Only)

SECOND EDITION

CORPORATE HEADQUARTERS UTICA, NEW YORK 13503

\*Trademark of Mohawk Data Sciences Corp., Utica, N.Y., Mohawk Data Sciences—Canada, Ltd. Registered User. Form No. 1948–11774 Mohawk Data Sciences Corp. Printed in U.S.A.

|                                | REV                             | ISION PAGE              |                            |

|--------------------------------|---------------------------------|-------------------------|----------------------------|

| EDITION/<br>ADDENDUM<br>NUMBER | NUMBER OF<br>SHEETS<br>AFFECTED | FORM NUMBER<br>AND DATE | SOFTWARE LEVI<br>SUPPORTED |

| EDITION 1                      |                                 | M-1948-1271             | Unknown                    |

| ADDENDUM 1                     |                                 | 11-1948-0372            | Unknown                    |

| ADDENDUM 2                     |                                 | M-1948-1072             | Unknown                    |

| ADDENDUM 3                     |                                 | M-1948-0173             | 03.00                      |

| ADDENDUM 4                     |                                 | M-1948-0673             | 03.00                      |

| ADDENDUM 5                     | 6                               | M-1948-1173             | 03.02                      |

| EDITION 2                      |                                 | PM-1948-0774            | 03.03                      |

|                                |                                 |                         |                            |

|                                |                                 |                         |                            |

|                                |                                 |                         |                            |

|                                |                                 |                         |                            |

|                                |                                 |                         |                            |

|                                |                                 |                         |                            |

|                                |                                 |                         |                            |

|                                |                                 |                         |                            |

|                                |                                 |                         |                            |

|                                |                                 |                         |                            |

|                                |                                 |                         |                            |

|                                |                                 |                         |                            |

| REASON FOR CURR                | ENT ADDENDUM/E                  | DITION:                 |                            |

| This edition combi             | nes edition 1 of                | this manual and editio  | n 1 of the                 |

| 2408 Instruction S             |                                 |                         |                            |

|                                |                                 |                         |                            |

|                                |                                 |                         |                            |

|                                |                                 |                         |                            |

|                                |                                 |                         |                            |

|                                |                                 |                         |                            |

|                                |                                 |                         |                            |

# TABLE OF CONTENTS

| Forward                                        |

|------------------------------------------------|

| Abbreviations And Conventions                  |

| Summary Of Instructions By Function            |

| Summary Of Instructions By Octal Sequence      |

|                                                |

| SECTION I. INTRODUCTION                        |

| Functions and Operations                       |

| Format for Instruction Descriptions            |

| Format for Instructions                        |

| Condition Designators                          |

| Binary Number Signs                            |

| Decimal Number Signs                           |

| Functions and Operations                       |

| Data Move                                      |

| Branching                                      |

| Compare                                        |

| Test                                           |

| Input/Output                                   |

| General Purpose                                |

| Logical                                        |

| Binary Arithmetic                              |

| Decimal Arithmetic                             |

| Sequential Editing                             |

| Interrupt                                      |

| External Execute Instruction Set               |

| Multiply/Divide Instructions                   |

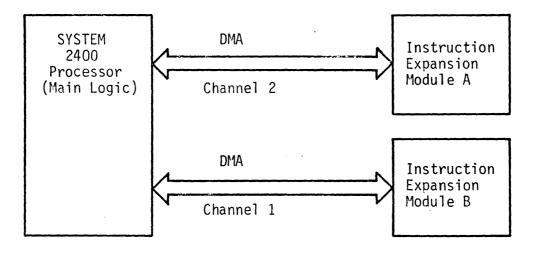

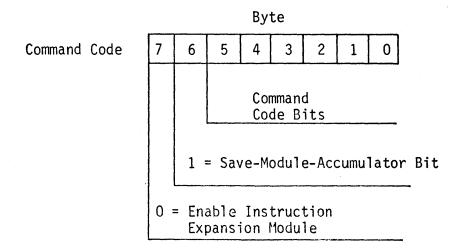

| Instruction Expansion Modules (General) 1-144  |

| Channel Assignments                            |

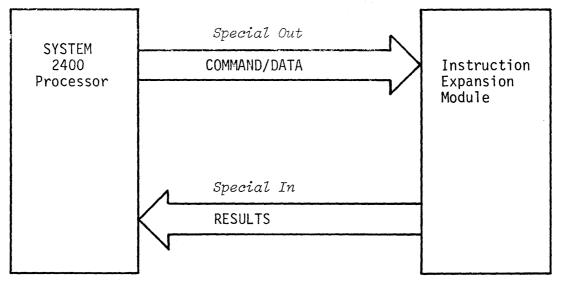

| Information Transfer                           |

| Instruction Expansion Module A (General) 1-147 |

| Program Call                                   |

| Instruction Expansion Module 3 (General)       |

| Logical Set                                    |

| Enter Store                                    |

1

PAGE

# TABLE OF CONTENTS (cont'd)

$\overline{}$

| SECTION II. | SYSTEM 2400 ASSEMBLER LANGUAGE                 | PAGE |

|-------------|------------------------------------------------|------|

|             | Introduction                                   | 2-1  |

|             | Coding Instructions                            | 2-2  |

|             | Symbolic Names                                 | 2-3  |

|             | Basic Instructions                             | 2-4  |

|             | Linkage Macros                                 | 2-10 |

|             | Operand Formats                                | 2-11 |

|             | Permissable Operands                           | 2-11 |

|             | Definition of Constants                        | 2-12 |

|             | Assembler Directives                           | 2-17 |

|             | Editing Source Input                           | 2-30 |

|             | Relocatability                                 | 2-31 |

|             | Error Flags In Listings                        | 2-32 |

|             | Modes of Operation                             | 2-32 |

|             | Operating The Assembler                        | 2-34 |

|             | Device Configuration                           | 2-36 |

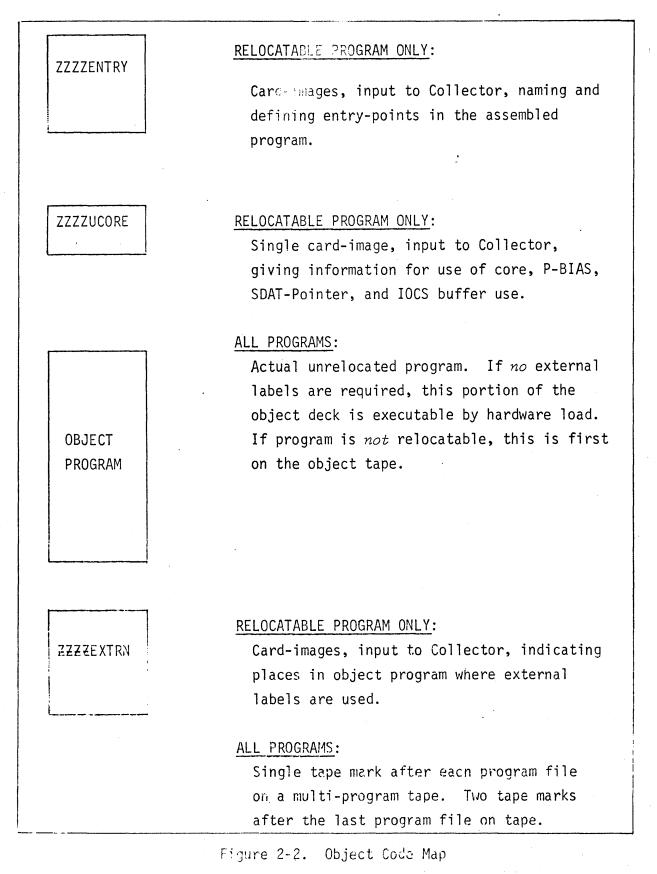

|             | Object Code Map                                | 2-37 |

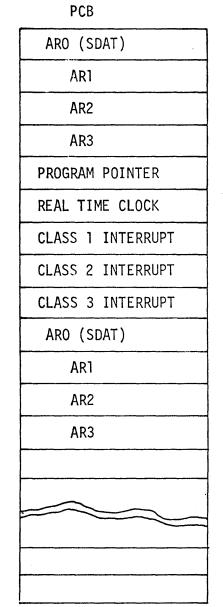

| APPENDIX A. | INTERRUPT PROGRAMMING                          |      |

|             | Software Interrupt Linkage                     | A-1  |

|             | Worker/Executive State                         |      |

|             | Enable/Disable Interrupts                      |      |

|             | Set/Clear Interrupt Lockout                    |      |

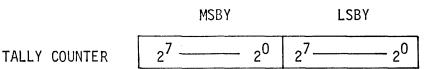

|             | Save Condition Designators & Tally Counter     | A-4  |

|             | Class 1 - Monitor Interrupts                   | A-5  |

|             | Class 2 - Service Interrupts                   |      |

|             | Class 3 - Special Interrupts                   |      |

| APPENDIX B. | PROGRAMMING ACTIVE RECORDS                     |      |

| APPENDIX C. | EBEDIC CODE                                    |      |

| APPENDIX D. | TALLY COUNTER                                  |      |

| APPENDIX E. | INSTRUCTION EXECUTION TIMES & PROCESSOR MODELS |      |

# TABLE OF CONTENTS (cont'd)

|             | F                                  | PAGE |

|-------------|------------------------------------|------|

| APPENDIX F. | OCTAL NOTATION RULES               |      |

|             | Octal/Decimal Conversion Procedure | F-1  |

|             | Tri-Octal Notation                 | F-3  |

| APPENDIX G. | SNAP P ADAPTER                     |      |

|             | Capture P                          | G-1  |

|             | Interrupt                          | G-2  |

| APPENDIX H. | UTILITY ADAPTER                    |      |

|             | General                            | H-1  |

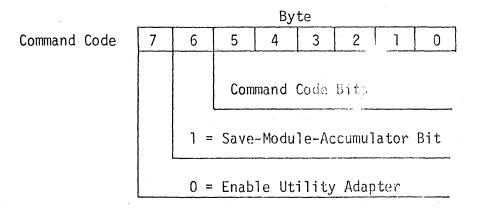

|             | Command Codes                      | H-2  |

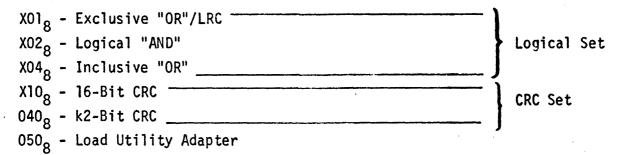

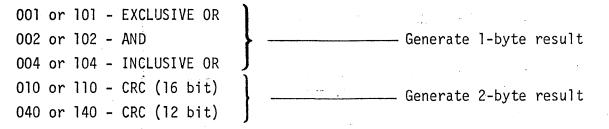

|             | Logical Set Feature                | H-3  |

|             | CRC Set                            | H-5  |

|             | Load Utility Adapter               | H-6  |

|             | Command Byte Modifiers (X)         | H-6  |

|             | Real Time Clock                    | H-6  |

#### LIST OF ILLUSTRATIONS

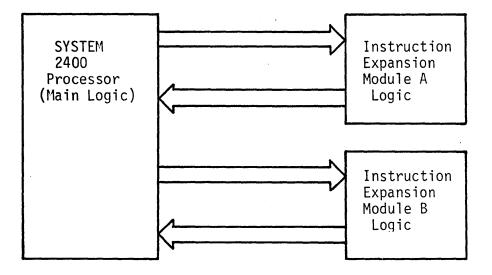

| Figure 1-1. | SYSTEM 2400 Processor Instruction Expansion Modules 1-144   |

|-------------|-------------------------------------------------------------|

| Figure 1-2. | Instruction Expansion Modules - Channel Configuration 1-145 |

| Figure 1-3. | Information Transfer                                        |

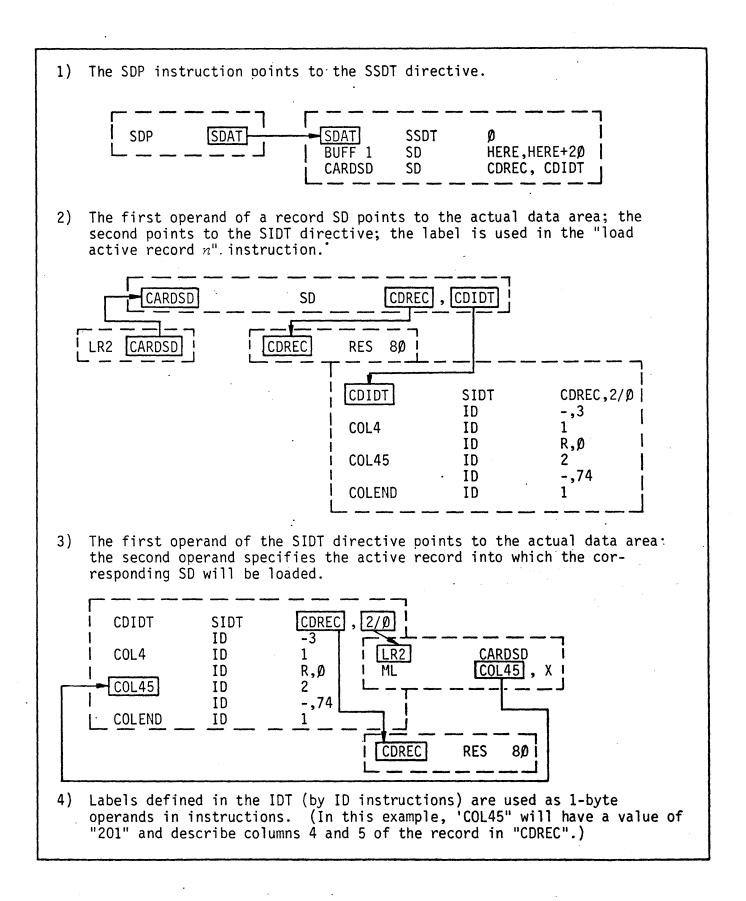

| Figure 2-1. | Use of SDAT and IDT                                         |

| Figure 2-2. | Object Code Map                                             |

| Figure A-1. | 2408 Processor - Program Control Block                      |

| Figure A-2. | Tally Counter.         A-5                                  |

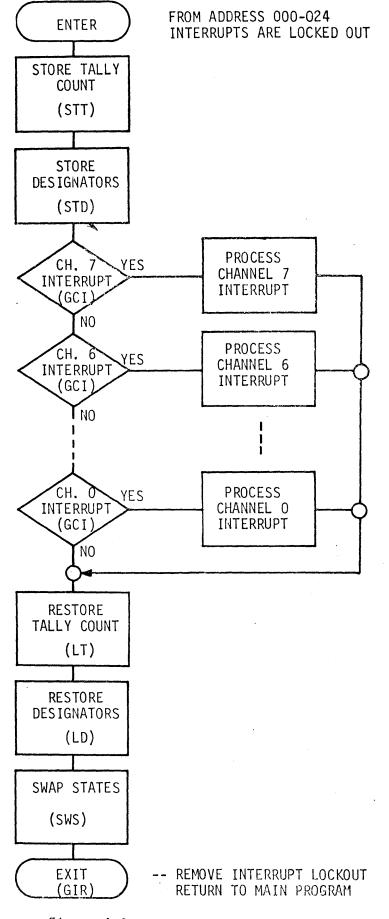

| Figure A-3. | Monitor Interrupt Processing Flow Diagram (Example) A-7     |

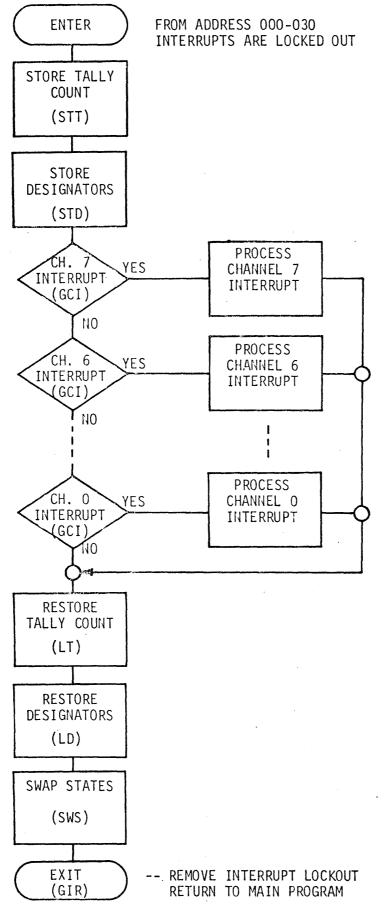

| Figure A-4. | Service Interrupt Processing Flow Diagram (Example) A-9     |

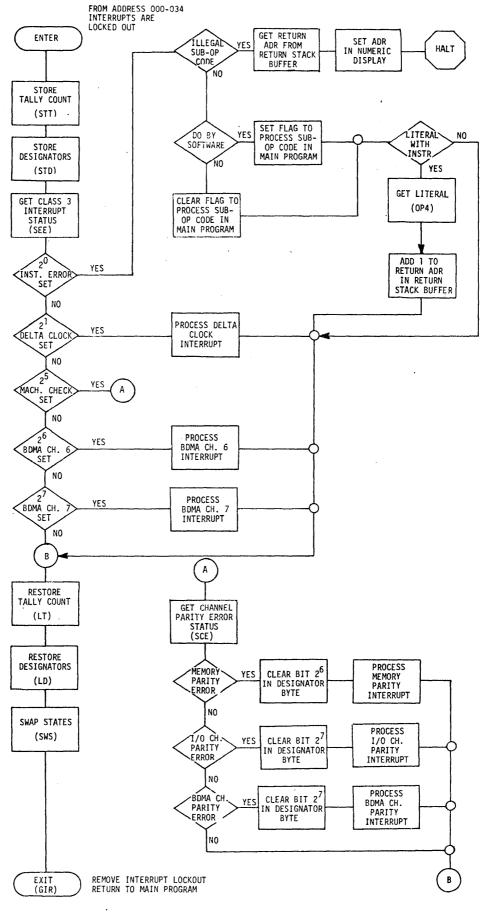

| Figure A-5. | Special Interrupt Processing Flow Diagram (Example) A-11    |

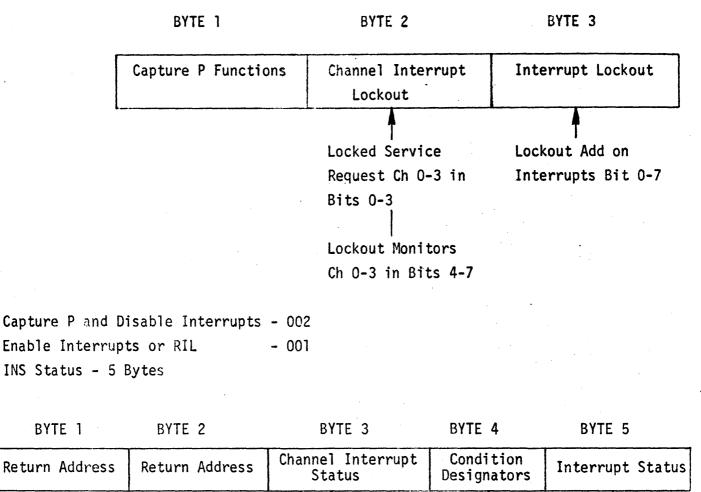

| Figure G-1. | OTS, ITEM 2, Three Bytes                                    |

| Figure G-2. | OTS, ITEM 2, Byte 2 Bit Assignments                         |

| Figure G-3. | OTS, ITEM 2, Byte 3 Bit Assignments                         |

| Figure G-4. | INS, ITEM 2 Bytes                                           |

| Figure G-5. | INS, ITEM 2, Byte 3 Bit Assignments                         |

#### LIST OF ILLUSTRATIONS (cont'd)

|        |       |                                      | Page |

|--------|-------|--------------------------------------|------|

| Figure | G-6.  | INS, ITEM 2, Byte 4 Bit Assignments  | G-5  |

| Figure | G-7.  | INS, ITEM 2, Byta 5 Bit Assignments  | G-6  |

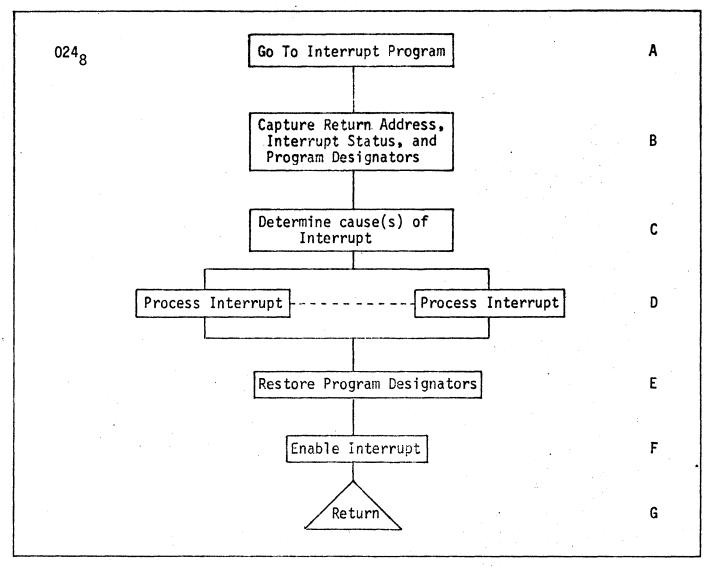

| Figure | G-8.  | Interrupt Processing Sequence        | G-7  |

| Figure | G-9.  | A Sample Restore Designators Routine | G-8  |

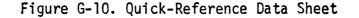

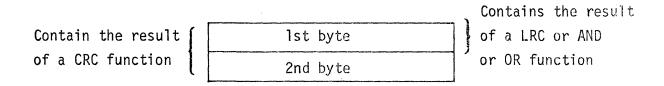

| Figure | G-10. | Quick-Reference Data Sheet           | G-9  |

#### LIST OF TABLES

| Table 2-1 | Basic Instructions                             |

|-----------|------------------------------------------------|

| Table 2-2 | Summary of Operands                            |

| Table 2-3 | Assembler Syntax Error Flags                   |

| Table 2-4 | Use of Lights and Switches in Assembler        |

| Table 2-5 | Assembler Configurations                       |

| Table E-1 | Formular for Execution Times of 501A Processor |

| Table E-2 | Formular for Execution Times of 502 Processors |

| Table E-3 | Instruction Set and Processor Model            |

| Table F-1 | Binary/Octal Equivalents                       |

| Table F-2 | Decimal/Octal Conversion Table                 |

.

#### FOREWORD

This manual describes the instruction repertoire, format, and detailed information for programming the SYSTEM 2400 Processors in Machine Code and SYSTEM 2400 Assembly Language. For conventional purposes, the user should always program SYSTEM 2400 applications in Mohawk Data Language (MDL) or RPG II, both of which are fully supported by MDS.

This manual provides in-depth information to the experienced user regarding the machine-code instruction repertoire for the SYSTEM 2400 Processors. The Software Manual SYSTEM 2400 Processor Programming in Machine Code (Form No. M-2269) is prerequisite reading to this document. For the effective use of this manual, familiarity with the following publications will also be particularly helpful:

SYSTEM 2400 Processor Operator Control Panels Hardware Manual (Form No. M-2268)

2406 Systems Console Hardware Manual (Form No. M-1940)

The reader should be familiar with compatible data processing equipments and associated programming systems.

Users that elect to include the 2406 Systems Console within their system and to program applications without using MDL or RPG II can function satisfactorily with the set of machine-level instructions described herein. This document contains the instruction formats and detailed steps for their use within the following functional categories:

- Data move

- Branching

- Compare

- Test

- Input/output

- General Purpose

- Logical

- Binary Arithmetic

- Decimal Arithmetic

- Sequential Editing

۷

- Interrupt

- External Execute

- Instruction Expansion Module A

- Instruction Expansion Module B

As a general rule, instructions preceded by an asterisk (\*) may only be used with a 502 Processor. While the instructions not preceded by an asterisk may be used with a 501 or 502 Processor. For detailed information on which processor can execute each instructions, see Appendix E.

#### ABBREVIATIONS AND CONVENTIONS

١

The following abbreviations and conventions are used when describing the instruction format and presenting typical examples:

| AR               | Active Record                 |

|------------------|-------------------------------|

| В                | Buffer                        |

| I                | Item                          |

| f                | Denotes an "off" condition    |

| IDT              | Item Descriptor Table         |

| Li               | Literal to be ignored         |

| L <sub>f</sub>   | Fill literal                  |

| Ls               | Sentinel literal              |

| LSD              | Least significant digit       |

| M                | Mask                          |

| MSB              | Most significant bit          |

| MSBY             | Most significant byte         |

| n                | Null                          |

| 0                | Denotes an "on" condition     |

| 00               | Operation Code                |

| OP1-4            | Operands 1 through 4          |

| PBIAS            | Program Bias                  |

| РСВ              | Program Control Block         |

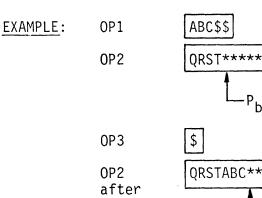

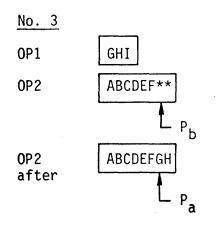

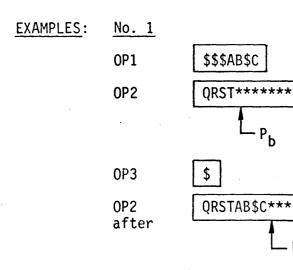

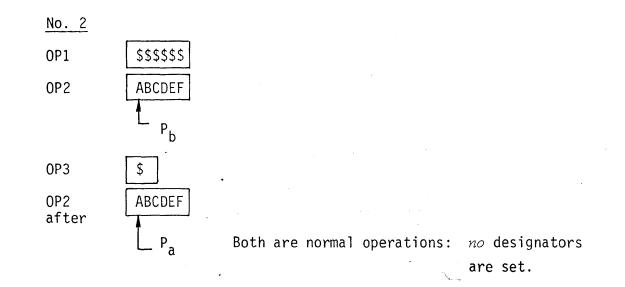

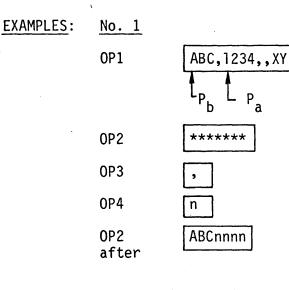

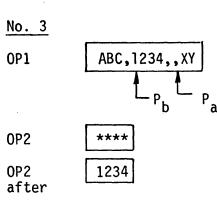

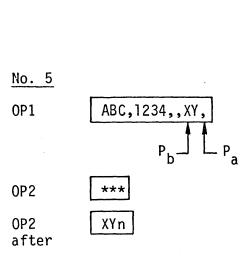

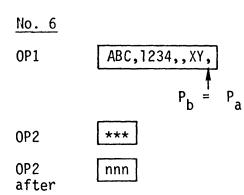

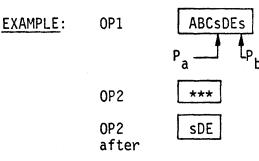

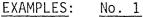

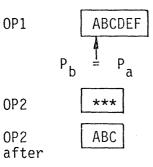

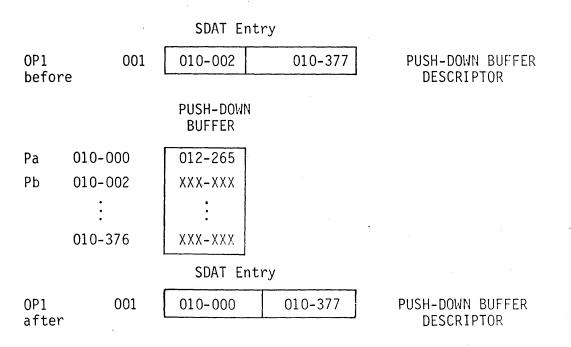

| Pa               | Pointer after an execution    |

| Р <sub>b</sub>   | Pointer before an execution   |

| R                | Record                        |

| S                | Space                         |

| SDAT             | Storage Descriptor Area Table |

| Z                | Zero                          |

| =                | Equals                        |

| +                | Not equal to                  |

| >                | Greater than                  |

| <                | Less Than                     |

| 2                | Equal to or Greater Than      |

| ><br><<br>-<br>+ | Equal to or Less Than         |

| +                | Plus                          |

| -                | Minus                         |

.

#### SUMMARY OF INSTRUCTIONS BY FUNCTION

|           | Op Code          |       | Page |                                     |     |       | Format |      |     |

|-----------|------------------|-------|------|-------------------------------------|-----|-------|--------|------|-----|

|           | Octal            | Mnem. | No.  | Instruction                         | ·0C | OP1   | 0P2    | OP3  | 0P4 |

|           | 000              | М     | 1-7  | Move Item, Left-<br>Align, No Fill  | 000 | AR/I  | AR/I   |      |     |

|           | 001              | MR    | 1-8  | Move Item, Right-<br>Align, No Fill | 001 | AR/I  | AR/I   |      |     |

|           | 003              | MED   | 1-9  | Move Item, Edit                     | 003 | AR/I  | AR/I   | ĄR∕I | L   |

|           | 004              | MF    | 1-10 | Move Item, Left-<br>Align, Fill     | 004 | AR/I  | AR/ I  | L    |     |

| MOVE      | 005              | MRF   | 1-11 | Move Item, Right-<br>Align, Fill    | 005 | AR/I  | AR/I   | L    |     |

| DATA M    | 006              | MJ    | 1-12 | Move Item, Left-<br>Justify, Fill   | 006 | AR/ I | AR/I   | ۰L   |     |

|           | 007              | MRJ   | 1-13 | Move Item, Right-<br>Justify, Fill  | 007 | AR/I  | AR/I   | L    |     |

|           | 050 <sub>.</sub> | MPK   | 1-14 | Move, Pack                          | 050 | AR/I  | AR/I   |      |     |

|           | 052              | MUP   | 1-15 | Move, Unpack                        | 052 | AR/I  | AR/I   |      |     |

|           | 140              | TRL . | 1-16 | Translate Code                      | 140 | AR/I  | AR/I   | AR/I |     |

|           | 141              | ML    | 1-17 | Move Literal                        | 141 | AR/I  | L      |      |     |

|           | 020              | NOP   | 1-19 | No Operation                        | 020 | add   | ress   |      |     |

|           | 021              | GGT   | 1-20 | GOTO Greater Than                   | 021 | add   | ress   |      |     |

|           | 022              | GLT   | 1-21 | GOTO Less Than                      | 022 | add   | ress   |      |     |

|           | 023              | GNE   | 1-22 | GOTO Not Equal                      | 023 | add   | ress   |      |     |

| IJ        | 024              | GE    | 1-23 | GOTO Equal                          | 024 | add   | ress   |      |     |

| CHIN      | 025              | GNL   | 1-24 | GOTO Not Less Than                  | 025 | add   | ress   |      |     |

| BRANCHING | 026              | GNG   | 1-25 | GOTO Not Greater<br>Than            | 026 | add   | ress   |      |     |

|           | 027              | G     | 1-26 | GOTO Unconditionally                | 027 | add   | ress   |      |     |

|           | 030              | GD    | 1-27 | GOTO On Designators                 | 030 | M     | add    | ress |     |

|           | 031              | GS    | 1-28 | GOTO On Switches                    | 031 | м     | add    | ress |     |

\* 502 Mode only

|           | Op Code          |             | Page |                                          | Format |      |      |      |     |

|-----------|------------------|-------------|------|------------------------------------------|--------|------|------|------|-----|

|           | Octal            | Mnem.       | No.  | Instruction                              | 00     | OP1  | 0P2  | 0P3  | OP4 |

|           | 061              | <b>G</b> BG | 1-29 | GOTO Binary Greater<br>Than              | 061    | AR/I | add  | ress |     |

|           | 062              | GBL         | 1-30 | GOTO Binary Less Than                    | 062    | AR/I | add  | ress |     |

|           | 063              | GBN         | 1-31 | GOTO Binary Non-Zero                     | 063    | AR/I | add  | ress |     |

|           | 064              | GBZ         | 1-32 | GOTO Binary Zero                         | 064    | AR/I | add  | ress |     |

|           | 065              | GGBE        | 1-33 | GOTO Binary <u>&gt;</u> Zero             | 065    | AR/I | add  | ress |     |

|           | 066              | GLBE        | 1-34 | GOTO Binary <u>&lt;</u> Zero             | 066    | AR/I | add  | ress |     |

| IJ        | 071              | GDG         | 1-35 | GOTO Decimal Greater<br>Than             | 071    | AR/I | add  | ress |     |

| BRANCHING | 072              | GDL         | 1-36 | GOTO Decimal Less<br>Than                | 072    | AR/I | add  | ress |     |

| BR        | 073              | GDN         | 1-37 | GOTO Decimal Non-Zero                    | 073    | AR/I | add  | ress |     |

|           | 074 <sup>.</sup> | GDZ         | 1-38 | GOTO Decimal Zero                        | 074    | AR/I | add  | ress |     |

|           | 075              | GGDE        | 1-39 | GOTO Decimal <u>&gt;</u> Zero            | 075    | AR/I | add  | ress | -   |

|           | 076              | GLDE        | 1-40 | GOTO Decimal <u>&lt;</u> Zero            | 076    | AR/I | add  | ress |     |

|           | 170              | GCT         | 1-41 | GOTO On Count                            | 170    | AR/I | add  | ress |     |

|           | 172              | GTB         | 1-42 | GOTO Table<br>(Indirect Branch)          | 172    | AR/I | AR/I | L    |     |

|           | 173              | GRT         | 1-44 | GOTO Return (Branch)                     | 173    | В    |      |      |     |

|           | 176              | GSB         | 1-45 | GOTO <sup>·</sup> Subroutine<br>(Branch) | 176    | В    | add  | ress |     |

|           | 044              | CB          | 1-47 | Compare Binary                           | 044    | AR/I | AR/I |      |     |

| RE        | 046              | CD          | 1-48 | Compare Decimal                          | 046    | AR/I | AR/I |      |     |

| COMPARE   | 142              | CAN         | 1-49 | Compare Alphanumerics                    | 142    | AR/I | AR/I |      |     |

| Ū         | 144              | CL          | 1-50 | Compare Literal                          | 144    | AR/I | L    |      |     |

IΧ

# SUMMARY OF INSTRUCTIONS

#### BY FUNCTION

;

(continued)

| 1            | Op Code           |                 | Page |                                   | Format      |       |       |       |     |

|--------------|-------------------|-----------------|------|-----------------------------------|-------------|-------|-------|-------|-----|

| 1            | Octal             | Mnem.           | No.  | Instruction                       | . 00        | 0P1   | 0P2   | 0P3   | 0P4 |

|              | 040               | TBS             | 1-52 | Test Binary Sign 🐇                | 040         | AR/I  |       |       |     |

|              | 042               | TDS             | 1-53 | Test Decimal Sign                 | 042         | AR/I  |       |       |     |

| TEST         | 150               | TI              | 1-54 | Test Item                         | 150         | AR/I  | AR/I  |       |     |

|              | 151               | TL              | 1-55 | Test Literal                      | 151         | AR/I  | L     |       |     |

|              | 152               | TM              | 1-56 | Test Mask                         | 152         | AR/I  | М     |       |     |

|              | *153              | TIM             | 1-57 | Test Item Mask                    | 153         | AR/I  | AR/I  |       |     |

|              | 100               | INS             | 1-60 | Special In                        | <b>10</b> 0 | AR/I  | AR/I  |       |     |

|              | 104               | EF              | 1-61 | External Function On<br>Channel   | 104         | AR/ I | AR/I  | AR/I  |     |

|              | 105               | OTS             | 1-62 | Special Out                       | 105         | AR/I  | AR/ I |       |     |

|              | *106 <sub>.</sub> | EFS             | 1-63 | External Function<br>Special      | 106         | AR/ I | AR/I  | AR/ I |     |

|              | 107               | GA .            | 1-64 | GOTO On Active<br>Channel         | 107         | AR/I  | addı  | ess   |     |

| 5            | 110               | STC             | 1-65 | Store Channel Control<br>Register | 110         | AR/I  | AR/I  |       |     |

| DUTPI        | *111              | STR             | 1-66 | Store Channel Reverse             | 111         | AR/I  | AR/I  |       |     |

| INPUT/OUTPUT | *112              | INR             | 1-67 | Initiate Input<br>Reverse         | 112         | AR/I  | В     |       |     |

|              | 114               | IN <sub>.</sub> | 1-68 | Initiate Input On<br>Channel      | 114         | AR/I  | В     |       |     |

|              | 115               | OUT             | 1-69 | Initiate Output On<br>Channel     | 115         | AR/I  | В     |       |     |

|              | *116              | OTR             | 1-70 | Initiate Output<br>Reverse        | 116         | AR/I  | В     |       |     |

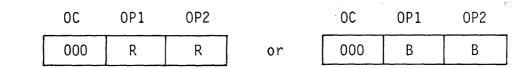

|              | 000               | RN              | 1-72 | Rename                            | 000         | B/R   | B/R   |       |     |

| ERAL<br>20SE | *124<br>*126      | STD             | 1-73 | Store Designators                 | 124         | AR/I  |       |       |     |

| GENE         | *126              | LD              | 1-74 | Load Designators                  | 126         | AR/I  |       |       |     |

\* 502 Mode only

Х

| 1              | Op Code |       | Page |                                    | Format |      |      |      |     |

|----------------|---------|-------|------|------------------------------------|--------|------|------|------|-----|

|                | Octal   | Mnem. | No.  | Instruction                        | 00     | 0P1  | 0P2  | 0P3  | 0P4 |

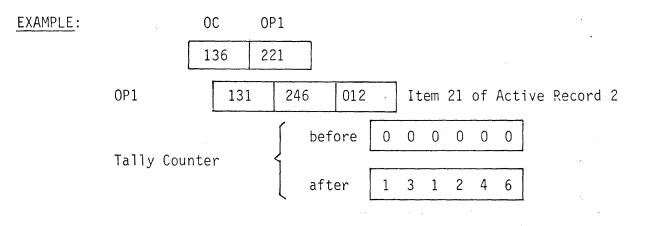

|                | 134     | STT   | 1-75 | Store Tally Counter                | 134    | AR/I |      |      |     |

|                | 136     | LT    | 1-76 | Load Tally Counter                 | 136    | AR/I |      |      |     |

|                | 143     | Н     | 1-77 | Halt                               | 143    |      |      |      |     |

|                | 146     | SDI   | 1-78 | Set Display<br>Indicators          | 146    | AR/I |      |      |     |

| SE             | 147     | GAP   | 1-79 | No Operation-Leave<br>Gap          | 147    |      |      |      |     |

| PURPOSE        | 156     | CDI   | 1-80 | Clear Display<br>Indicators        | 156    | AR/I |      |      |     |

| <b>GENERAL</b> | 161     | LSP   | 1-81 | Load Storage<br>Descriptor Pointer | 161    | SDP  |      |      |     |

| 9              | 165     | LR1   | 1-82 | Load Active Record 1               | 165    | R    |      |      |     |

|                | 171     | LR2   | 1-82 | Load Active Record 2               | 171    | R    |      |      |     |

|                | 175     | LR3   | 1-82 | Load Active Record 3               | 175    | R    |      |      |     |

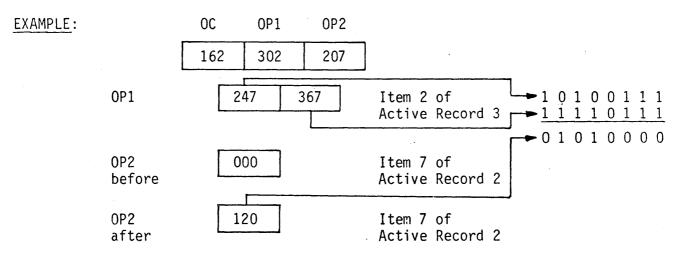

|                | 160     | χ.    | 1-84 | OR (Exclusive)                     | 160    | AR/I | AR/I | AR/I |     |

| LOGICAL        | 162     | RCK   | 1-85 | Longitudinal<br>Redundancy Check   | 162    | AR/I | AR/I |      |     |

| LOG            | 164     | 0     | 1-86 | OR (Inclusive)                     | 164    | AR/I | AR/I | AR/I |     |

|                | 166     | N     | 1-87 | Logical AND                        | 166    | AR/I | AR/I | AR/I |     |

| TIC            | 041     | AB    | 1-89 | Add Binary                         | 041    | AR/I | AR/I | AR/I |     |

| ARITHMETIC     | 045     | SB    | 1-90 | Subtract Binary                    | 045    | AR/I | AR/I | AR/I |     |

|                | 051     | ALB   | 1-91 | Add Literal Binary                 | 051    | AR/I | AR/I | L    |     |

| BINARY         | 055     | SLB   | 1-92 | Subtract Literal<br>Binary         | 055    | AR/I | AR/I | L    |     |

| [          | Op Code Page<br>Octal Mnem. No. Instruction |                             | Page  | Page                                  |      | Format |      |                |                |  |

|------------|---------------------------------------------|-----------------------------|-------|---------------------------------------|------|--------|------|----------------|----------------|--|

|            |                                             |                             | .00   | 0P1                                   | 0P2  | OP3    | OP4  |                |                |  |

| LIC        | 043                                         | А                           | 1-94  | Add Decimal                           | 043  | AR/I   | AR/I | AR/I           |                |  |

| ARITHMETIC | 047                                         | 047 S 1-95 Subtract Decimal |       |                                       |      | AR/I   | AR/I | AR/I           |                |  |

| ARI        | 053                                         | AL                          | 1-96  | Add Literal Decimal                   | 053  | AR/I   | AR/I | L              |                |  |

| DECIMAL    | 057                                         | SL                          | 1-97  | Subtract Literal<br>Decimal           | 057. | AR/I   | AR/I | L              |                |  |

|            | 014                                         | СР                          | 1-100 | Compress Item, Left-<br>Align, Fill   | 014  | AR/I   | AR/Į | Li             | L <sub>f</sub> |  |

|            | 015                                         | CPR                         | 1-10] | Compress Item, Right-<br>Align, Fill  | 015  | AR/I   | AR/I | Li             | L <sub>f</sub> |  |

| .5         | 120                                         | APR                         | 1-102 | Append, Right-<br>Eliminate           | 120  | AR/I   | в.   | L              |                |  |

| EDITING    | 121                                         | APA                         | 1-103 | Append, Advance                       | 121  | AR/I   | В    |                |                |  |

|            | 122 <sub>.</sub>                            | APE                         | 1-105 | Append, Left-<br>Eliminate            | 122  | AR/I   | B    | L              |                |  |

| SEQUENTIAL | 130                                         | EXV.                        | 1-107 | Extract Variable<br>Length Item, Fill | 130  | В      | AR/I | L <sub>s</sub> | L <sub>f</sub> |  |

| SE         | 131                                         | EXP                         | 1-111 | Extract Previous Item                 | 131  | В      | AR/I |                |                |  |

|            | 132                                         | EX                          | 1-112 | Extract Item                          | 132  | В      | AR/I | -              |                |  |

|            | 133                                         | EXA                         | 1-114 | Extract Item, Advance                 | 133  | В      | AR/I |                |                |  |

|            | 113                                         | GSI                         | 1-117 | GOTO On Service<br>Request            | 113  | AR/I   | add  | ress           |                |  |

|            | 117                                         | GCI                         | 1-118 | GOTO On Channel .<br>Interrupt        | 117  | AR/I   | add  | ress           |                |  |

| Tq         | 154                                         | SWS                         | 1-119 | Swap States                           | 154  |        |      |                |                |  |

| INTERRUPT  | 155                                         | SIL                         | 1-120 | Set Interrupt Lockout                 | 155  |        |      |                |                |  |

| LNI        | 157                                         | CIL                         | 1-121 | Clear Interrupt<br>Lockout            | 157  |        |      |                |                |  |

|            | 174                                         | IM                          | 1-122 | Interrupt Mask                        | 174  | AR/I   |      |                |                |  |

|            | 177                                         | GIR                         | 1-124 | Interrupt Branch GOTO                 | 177  | В      |      |                |                |  |

\* 502 Mode only

.

| 1            | Op Code          |       | Page  |                                     | Format |         |      |       |     |

|--------------|------------------|-------|-------|-------------------------------------|--------|---------|------|-------|-----|

|              | Octal            | Mnem. | No.   | Instruction                         | 00     | 0P1     | 0P2  | 0P3   | OP4 |

|              | 004              | LC    | 1-127 | Load Delta Clock                    | 004    | AR/I    |      |       |     |

|              | 014              | SEE   | 1-128 | Store External<br>Instruction Error | 014    | <b></b> |      | AR/I  |     |

|              | 015              | SCE   | 1-131 | Store Channel<br>Parity Error       | 015    |         |      | AR/I  |     |

|              | 020              | MB    | 1-132 | Multiply Binary                     | 020    | AR/I    | AR/I | AR/I  |     |

| 145          | 021              | MLB   | 1-133 | Multiply Literal<br>Binary          | 021    | AR/I    |      | AR/ I | L   |

| <br>0C       | 022              | DB    | 1-134 | Divide Binary                       | 022    | AR/I    | AR/I | AR/I  |     |

| ONS          | 023              | DLB   | 1-135 | Divide Literal<br>Binary            | 023    | AR/ I   |      | AR/I  | L   |

| UCTI         | 024              | MD    | 1-136 | Multiply Decimal                    | 024    | AR/I    | AR/I | AR/I  |     |

| INSTRUCTIONS | 025 <sub>.</sub> | MLD   | 1-137 | Multiply Literal<br>Decimal         | 025    | AR/I    |      | AR/ I | L   |

| EXECUTE      | 026              | DD    | 1-138 | Divide Decimal                      | 026    | AR/I    | AR/I | AR/ I |     |

|              | 027              | DLD   | 1-139 | Divide Literal<br>Decimal           | 027    | AR/I    |      | AR/I  | L   |

| EXTERNAL     | 030              | BTD   | 1-140 | Binary to Decimal                   | 030    | AR/I    |      | AR/I  |     |

| ШX           | 031              | DTB   | 1-14] | Decimal to Binary                   | 031    | AR/I    |      | AR/I  |     |

|              | 034              | SDR   | 1-142 | Store Decimal<br>Remainder          | 034    |         |      | AR/I  |     |

|              | 035              | SBR   | 1-143 | Store Binary<br>Remainder           | 035    |         |      | AR/ I |     |

|                                | Op Code          |                  | Page  |                                    | Format |              |              |     |     |

|--------------------------------|------------------|------------------|-------|------------------------------------|--------|--------------|--------------|-----|-----|

|                                | Octal            | Mnem.            | No.   | Instruction                        | 00     | 0P1          | 0P2          | 0P3 | 0P4 |

| TON EXP-                       | 105              | SVP<br>or<br>SAP | 1-149 | Save (P)                           | 105    | AR/I<br>002  | AR/I<br>002  |     |     |

| INSTRUCTION E<br>ANSION MODULE | 100              | SRP              | 1-150 | Store (P)                          | 100    | AR/ I<br>002 | AR/ I        |     |     |

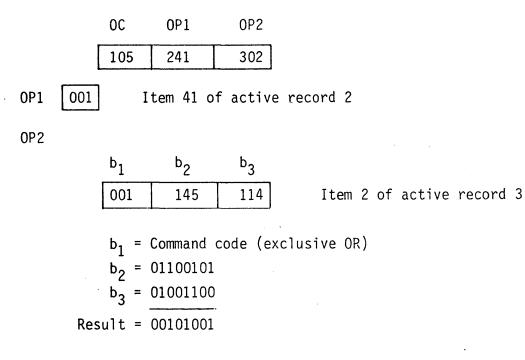

|                                | 105              | ORE              | 1-153 | OR (Exclusive)                     | 105    | AR/I<br>001  | AR/I<br>001  |     |     |

|                                | 105              | AND              | 1-154 | Logical AND                        | 105    | AR/I<br>001  | AR/ I<br>002 |     |     |

| EXPANSION<br>B                 | 105              | ORI              | 1-156 | OR (Inclusive)                     | 105    | AR/I<br>001  | AR/ I<br>004 |     |     |

| 1 11.8                         | 105              | LRC              | 1-158 | Longitudinal Re-<br>dundancy Check | 105    | AR/I<br>001  | AR/I<br>001  |     |     |

| INSTRUCTION<br>MODUL           | 105 <sup>.</sup> | EMA              | 1-160 | Enter Module<br>Accumulator        | 105    | AR/I<br>001  | AR/ I<br>050 |     |     |

|                                | 100              | SMA -            | 1-161 | Store Module<br>Accumulator        | 100    | AR/I<br>001  | AR/I         |     |     |

#### SUMMARY OF INSTRUCTIONS BY OCTAL SEQUENCE

•

| Octal       | Mnemonic | Page<br>No. | Instruction                      |  |  |

|-------------|----------|-------------|----------------------------------|--|--|

| 000         | RN       | 1-72        | Rename                           |  |  |

| 000         | м        | 1-7         | Move Item, Left-Align, No Fill   |  |  |

| 001         | MR       | 1-8         | Move Item, Right-Align, No Fill  |  |  |

| - 003       | MED      | 1-9         | Move Item, Edit                  |  |  |

| 004         | MF       | 1-10        | Move Item, Left-Align, Fill      |  |  |

| 005         | MRF      | 1-11        | Move Item, Right-Align, Fill     |  |  |

| 006         | MJ       | 1-12        | Move Item, Left-Justify, Fill    |  |  |

| .007        | MRJ      | 1-13        | Move Item, Right-Justify, Fill   |  |  |

| 014         | СР       | 1-99        | Compress Item, Left-Align, Fill  |  |  |

| 01 <u>5</u> | CPR      | 1-10        | Compress Item, Right-Align, Fill |  |  |

| 020         | NOP      | 1–19        | No Operation                     |  |  |

| 021         | . GGT    | 1-20        | GOTO Greater Than                |  |  |

| 022         | GLT      | 1-21        | GOTO Less Than                   |  |  |

| 023         | GNE      | 1-22        | GOTO Not Equal                   |  |  |

| 024         | GE       | 1-23        | GOTO Equal                       |  |  |

| 025         | GNL      | 1-24        | GOTO Not Less Than               |  |  |

| 026         | GNG      | ·<br>1-25   | GOTO Not Greater Than            |  |  |

| 027         | G .      | 1-26        | GOTO Unconditionally             |  |  |

| 030         | GD       | 1-27        | GOTO On Designators              |  |  |

| 031         | GS       | <b>1-28</b> | GOTO On Switches                 |  |  |

| 040         | TBS      | 1-52        | Test Binary Sign                 |  |  |

| 041         | AB       | 1-89        | Add Binary                       |  |  |

| 042         | TDS      | 1-53        | Test Decimal Sign                |  |  |

| 043         | А        | 1-94        | Add Decimal                      |  |  |

\* 502 Mode only.

XV

| Octal | Mnemonic | Page<br>No.    | Instruction                   |

|-------|----------|----------------|-------------------------------|

| 044   | СВ       | 1-47           | Compare Binary                |

| 045   | SB       | 1-90           | Subtract Binary               |

| 046   | CD       | 1-48           | Compare Decimal               |

| 047   | S        | 1-95           | Subtract Decimal              |

| *050  | МРК      | 1-14           | Move, Pack                    |

| 051   | ALB      | 1-91           | Add Literal Binary            |

| *052  | MUP      | 1-15           | Move, Unpack                  |

| 053   | AL       | 1-96           | Add Literal Decimal           |

| 055   | SLB      | 1-92           | Subtract Literal Binary       |

| 057   | SL       | 1-97           | Subtract Literal Decimal      |

| *061  | GBG      | 1-29           | GOTO Binary Greater Than      |

| *062  | GBL      | 1-30           | GOTO Binary Less Than         |

| *063  | GNB      | 1-31           | GOTO Binary Non-Zero          |

| *064  | GBZ      | 1-32           | GOTO Binary Zero              |

| *065  | GGBE     | 1-33           | GOTO Binary <u>&gt;</u> Zero  |

| *066  | GLBE     | 1-34           | GOTO Binary <u>&lt;</u> Zero  |

| *071  | GDG      | 1-35           | GOTO Decimal Greater Than     |

| *072  | GDL      | 1-36           | GOTO Decimal Less Than        |

| *073  | GDN      | 1-37           | GOTO Decimal Non-Zero         |

| *074  | GDZ      | 1-38           | GOTO Decimal Zero             |

| *075  | GGDE     | 1-39           | GOTO Decimal <u>&gt;</u> Zero |

| *076  | GLDE     | 1-40           | GOTO Decimal <u>&lt;</u> Zero |

| 100   | INS      | · <b>1-</b> 60 | Special In                    |

| 100   | SRP      | 1-150          | Store (P)                     |

\* 502 Mode only.

.

| Octal | Mnemonic   | Page<br>No. | Instruction                    |

|-------|------------|-------------|--------------------------------|

| 100   | SMA        | 1-161       | Store Module Accumulator       |

| 104   | EF         | · 1-61      | External Function On Channel   |

| 105   | OTS        | 1-62        | Special Out                    |

| 105   | SAP or SVP | 1-149       | Save (P)                       |

| 105   | ORE        | 1-153       | OR (Exclusive)                 |

| 105   | AND        | 1-154       | Logical AND                    |

| 105   | . ORI      | 1-156       | OR (Inclusive)                 |

| 105   | LRC        | 1-158       | Longitudinal Redundancy Check  |

| 105   | EMA        | 1-160       | Enter Module Accumulator       |

| *106  | EFS        | 1-63        | External Function Special      |

| 107   | GA         | 1-64        | GOTO On Active Channel         |

| 110   | STC        | 1-65        | Store Channel Control Register |

| *111  | STR        | 1-66        | Store Channel Reverse          |

| *112  | INR        | 1-67        | Initiate Input Reverse         |

| *113  | GSI        | 1-117       | GOTO On Service Request        |

| 114   | IN         | 1-68        | Initiate Input On Channel      |

| 115   | OUT        | 1–69        | Initiate Output On Channel     |

| *116  | OTR        | 1-70        | Initiate Output Reverse        |

| *117  | GC I       | 1-118       | GOTO On Channel Interrupt      |

| 120   | APR        | 1-102       | Append, Right-Eliminate        |

| . 121 | ΑΡΑ        | 1-103       | Append, Advance                |

| 122   | APE        | 1-105       | Append, Left-Eliminate         |

| Octal         | Mnemonic | Page<br>No. | Instruction                        |

|---------------|----------|-------------|------------------------------------|

| 124           | STD      | 1-73        | Store Designators                  |

| 126           | LD       | 1-74        | Load Designators                   |

| 130           | EXV      | 1-107       | Extract Variable Length Item, Fill |

| 131           | EXP      | 1-111       | Extract Previous Item              |

| 132           | EX       | 1-112       | Extract Item                       |

| 133           | EXA      | 1-114       | Extract Item, Advance              |

| 134           | STT      | 1-75        | Store Tally Counter                |

| 136           | LT       | 1-76        | Load Tally Counter                 |

| 140           | TRL      | 1-16        | Translate Code                     |

| 141           | ML ·     | 1-17        | Move Literal                       |

| 142           | CAN      | 1-49        | Compare Alphanumerics              |

| 143           | Н        | 1-77        | Halt                               |

| 144           | CL       | 1-50        | Compare Literal                    |

| *145<br>(004) | LC       | 1-127       | Load Delta Clock                   |

| *145<br>(014) | SEE      | 1-128       | Store External Instruction Error   |

| *145<br>(015) | SCE      | 1-131       | Store Channel Parity Error         |

| *145<br>(020) | MB .     | 1-132       | Multiply Binary                    |

| *145<br>(021) | MLB      | 1-133       | Multiply Literal Binary            |

| *145<br>(022) | DB       | 1-134       | Divide Binary                      |

| *145<br>(023) | DLB      | 1-135       | Divide Literal Binary              |

\* 502 Mode only.

| Octal         | Mnemonic | Page<br>No. | Instruction                     |

|---------------|----------|-------------|---------------------------------|

| *145<br>(024) | MD       | 1-136       | Multiply Decimal                |

| *145<br>(025) | MLD      | 1-137       | Multiply Literal Decimal        |

| *145<br>(026) | DD       | 1-138       | Divide Decimal                  |

| *145<br>(027) | DLD      | 1-139       | Divide Literal Decimal          |

| *145<br>(030) | BTD      | 1-140       | Binary to Decimal               |

| *145<br>(031) | DTB      | 1-141       | Decimal to Binary               |

| *145<br>(034) | SDR      | 1-142       | Store Decimal Remainder         |

| *145<br>(035) | SBR      | 1-143       | Store Binary Remainder          |

| 146           | SDI      | 1-78        | Set Display Indicators          |

| *147          | GAP      | 1-79        | No Operation-Leave Gap          |

| 150           | TI       | 1-54        | Test Item                       |

| 151           | TL       | 1-55        | Test Literal                    |

| 152           | ТМ       | 1-56        | Test Mask                       |

| *153          | TIM .    | 1-57        | Test Item Mask                  |

| *154          | SWS      | 1-119       | Swap States                     |

| *155          | SIL      | 1-120       | Set Interrupt Lockout           |

| 156           | CDI .    | 1-80        | Clear Display Indicators        |

| *157          | CIL      | 1-121       | Clear Interrupt Lockout         |

| *160          | х        | 1-84        | OR (Exclusive)                  |

| *161          | LSP      | 1-81        | Load Storage Descriptor Pointer |

\* 502 Mode only.

| Octal | Mnemonic | Page<br>No. | Instruction                   |

|-------|----------|-------------|-------------------------------|

| *162  | RCK      | 1-85        | Longitudinal Redundancy Check |

| *164  | 0        | 1-86        | OR (Inclusive)                |

| 165   | LR1      | 1-82        | Load Active Record 1          |

| *166  | N        | 1-87        | Logical AND                   |

| *170  | GCT      | 1-41        | GOTO On Count                 |

| 171   | LR2      | 1-82        | Load Active Record 2          |

| *172  | GTB      | 1-42        | GOTO Table (Indirect Branch)  |

| *173  | GRT      | 1-44        | GOTO Return (Branch)          |

| *173  | IM       | 1-122       | Interrupt Mask                |

| 175   | LR3      | 1-82        | Load Active Record 3          |

| *176  | GSB      | 1-45        | GOTO Subroutine (Branch)      |

| *177  | GIR      | 1-124       | Interrupt Branch GOTO         |

#### SECTION I

#### SYSTEM 2400 MACHINE CODE

This section describes the total SYSTEM 2400 machine - level instruction set. Each instruction has a variable-length format, with

• an op code, to specify the operation to be performed,

and

• zero-to-four operands, to specify the records, items, buffers, etc., to be operated upon.

The op code and operands are each 1-byte long, with the op code first,

# Op Code OP1 OP2 OP3 OP4

followed by the operands arranged in the prescribed sequence for a given instruction. Op codes and operands are expressed in octal notation.

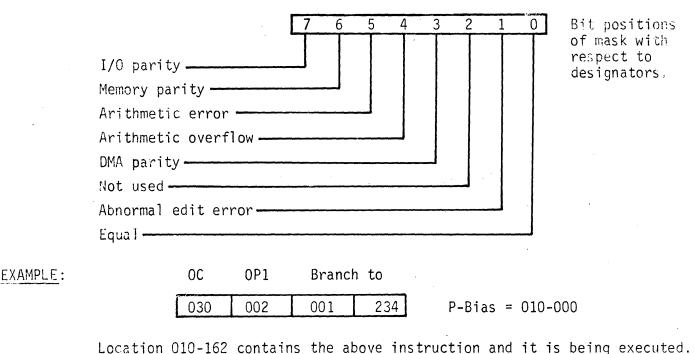

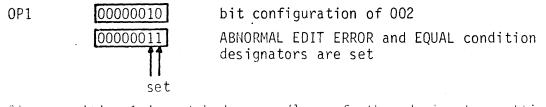

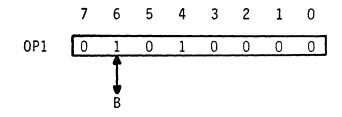

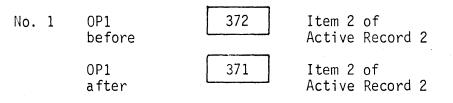

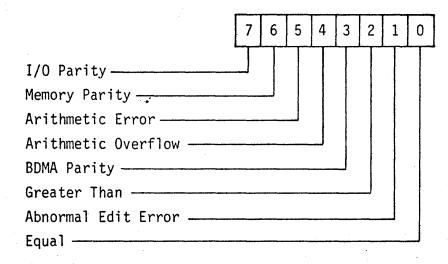

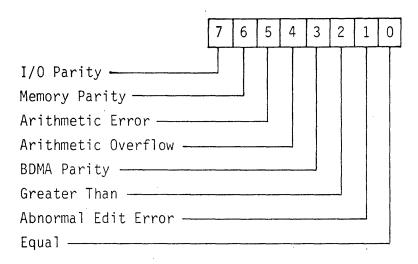

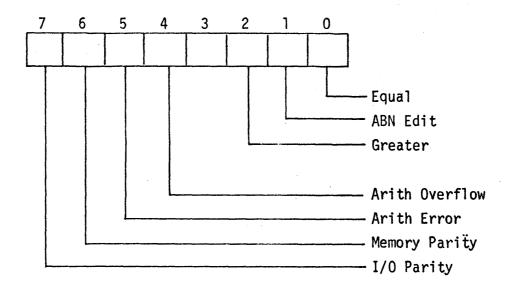

#### CONDITION DESIGNATORS

Condition Designators denote

● =, **+**, >, <

and

• arithmetic and abnormal-edit errors.

The Compare and the Test instructions establish conditions and set the appropriate internal condition designators, which are used by the Branching instructions to branch from the instruction execution sequence. Many of the Sequential Editing instructions set the Equal designator to indicate when the end of a data trnasfer to or from a working buffer has occurred. They also set the abnormal-edit designator to indicate when the receiving area in a data transfer is too small. Both the arithmetic overflow and the arithmetic error designators denote errors caused by a Binary or a Decimal Arithmetic instruction. The designators remain set throughout program execution until they are reset by subsequent instructions.

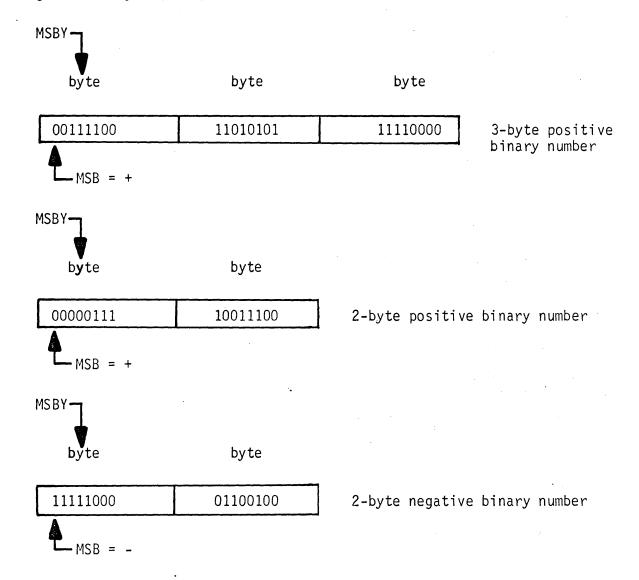

#### BINARY NUMBER SIGNS

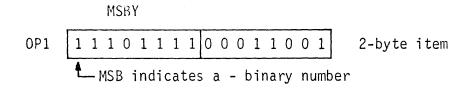

The sign of a binary number is indicated by the most significant bit (MSB) of the most significant byte (MSBY) of the item: 0 = + and 1 = -.

All the negative binary numbers coded into the binary-oriented instructions *must be* in the two's complement form. To convert a binary number

0 0 1 0 1 0 1 0 1 0into two's complement notation,change each bit1 1 0 1 0 1 0 1to its opposite state (- one's complement)and add 11to produce itstwo's complement.1 1 0 1 0 1 1 0

1-2

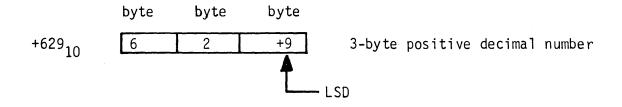

#### DECIMAL NUMBER SIGNS

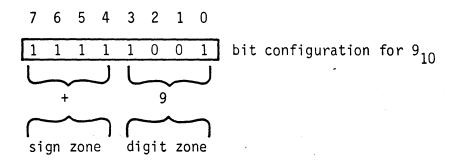

In decimal arithmetic, the sign of a number is indicated by the sign of the least significant digit, as shown below.

The plus sign for the digit is expressed as "1111" in the sign zone (left half) of the LSD  $(9_{10})$  byte (position 7654).

For a minus number, such as

6

-629<sub>10</sub>

3-byte negative decimal number,

The minus sign for the digit is expressed as 1101 in the sign zone of the LSD byte, as shown below.

-9

2

7 6 5 4 3 2 1 0 1 1 0 1 1 0 0 1 bit configuration for  $-9_{10}$

In the SYSTEM 2400 EBCDIC character set, the negative numbers correspond to the binary configurations for the letters J through R, as noted below.

| Bin  | ary  | or | <u>Octal</u> | = | Number | and Corresponds to |

|------|------|----|--------------|---|--------|--------------------|

| 1101 | 0001 |    | 321          |   | -1     | J                  |

| 1101 | 0010 |    | 322          |   | -2     | К                  |

| 1101 | 0011 |    | 323          |   | -3     | L                  |

| 1101 | 0100 |    | 324          |   | -4     | М                  |

| 1101 | 0101 |    | 325          |   | -5     | N                  |

| 1101 | 0110 |    | 326          |   | -6     | 0                  |

| 1101 | 0111 |    | 327          |   | -7     | Р                  |

| 1101 | 1000 |    | 330          |   | -8     | Q                  |

| 1101 | 1001 |    | 331          |   | -9     | R                  |

#### FUNCTIONS AND OPERATIONS

Each machine-code instruction is functionally categorized into one of the following:

- Data Move (1-6): transfer a copy of a complete data string.

- Branching (1-18): conditional or unconditional branching from the normal program sequence.

- Compare (1-46): compare data strings.

- Test (1-51): test for the sign or identity of an item.

- Input/Output (1-59): initiate and control input/output operations.

- General Purpose (1-71): perform various operational functions.

- Logical (1-83): AND, OR, or Exclusive OR.

- Binary Arithmetic (1-88): add and subtract in binary

- Decimal Arithmetic (1-93): add and subtract in decimal.

- Sequential Editing (1-98): manipulate data as it is transferred between peripherals.

- Interrupt (1-116): interpret, control and process events that divert the processor from main program execution.

- External Execute (1-125): instructions added by hardware expansion modules to provide the following functions:

- a. Multiply and Divide

- b. Binary/Decimal Conversion

- c. Delta Clock

- d. Channel Parity Error Determination

- Instruction Expansion Modules A and B (1-144).

Individual instructions are described as follows:

FUNCTIONAL CATEGORY Descriptive Name of Instruction Mnemonic Op Code = ABC Octal Op Code = 123

<u>PURPOSE</u>: Brief explanation of what the instruction does.

FORMAT: Format of the instruction.

OPERATION: Operation of the instruction and the programming details.

EXAMPLE: Typical example that uses the instruction.

#### DATA MOVE

The Data Move instructions move a copy of OP1 item to OP2 item, character-bycharacter; OP1 item remains unchanged. The move is terminated when all of OP1 item is copied or when OP2 item is full. When OP2 item is longer than OP1 item, the excess positions are unchanged by the move operation, unless a fill operation is specified.

Left-justification means omit copying the *leading* nulls, spaces, and zeros and left-align the entry into the OP2 item with a character fill.

Right-justification means omit copying the *trailing* spaces and nulls (not zeros) and right-align the entry into the OP2 item with a character fill.

The Data Move instructions include the following:

- Move Item, Left Align, No Fill (1-7)

- Move Item, Right Align, No. Fill (1-8)

- Move Item, Edit (1-9)

- Move Item, Left Align, Fill (1-10)

- Move Item, Right Align, Fill (1-11)

- Move Item, Left Justify, Fill (1-12)

- Move Item, Right Justify, Fill (1-13)

- Move, Pack (1-14)

- Move, Unpack (1-15)

- Translate Code (1-16)

- Move Literal (1-17)

#### DATA MOVE Move Item, Left-Align, No Fill Mnemonic Op Code = M Octal Op Code = 000

- <u>PURPOSE</u>: To copy the data from one item to another, with the content of the receiving item left-aligned.

- FORMAT:OCOIOP2000AR/IAR/I

- <u>OPERATION</u>: A copy of the contents of the OP1 item is moved left-aligned into the OP2 item. If OP2 is larger than OP1, the remaining characters are unaffected. If OP1 is larger than OP2, the extra OP1 characters at the right are truncated.

| EXAMPLES: | <u>No. 1</u> | 0C 0P1    | OP2                        |

|-----------|--------------|-----------|----------------------------|

|           |              | 000 102   | 211                        |

|           | 0P1          | AsBCDEF   | Item 2 of Active Record 1  |

|           | 0P2          | RICHARDsG | Item 11 of Active Record 2 |

|           | OP2<br>after | AsBCDEFsG | Item 11 of Active Record 2 |

|           | 0P1<br>after | AsBCDEF   | Item 2 of Active Record 1  |

|           | <u>No. 2</u> | OC OP1    | 0P2<br>211                 |

|           | 0P1          | AsBCDEF   | Item 2 of Active Record 1  |

|           | 0P2          | PQRS      | Item 10 of Active Record 2 |

|           | OP2<br>after | AsBC      | Item 10 of Active Record 2 |

|           | OP1<br>after | AsBCDEF   | Item 2 of Active Record 1  |

1-7

#### DATA MOVE Move Item, Right-Align, No Fill Mnemonic Op Code = MR Octal Op Code = 001

<u>PURPOSE</u>: To copy the data from one item to another, with the content of the receiving item right-aligned.

| FORMAT: | 00  | 0P1  | 0P2  |

|---------|-----|------|------|

|         | 001 | AR/I | AR/I |

<u>OPERATION</u>: A copy of the contents of the OP1 item is moved right-aligned into the OP2 item. If OP2 is larger than OP1, the remaining characters are unaffected. If OP1 is larger than OP2, the extra OP1 characters at the left are truncated.

| EXAMPLES: | <u>No. 1</u>     | 00      | 0P1 | OP2                        |

|-----------|------------------|---------|-----|----------------------------|

|           |                  | 001     | 102 | 211                        |

|           |                  |         |     |                            |

|           | OP1 AsI          | BCDEF   |     | Item 2 of Active Record 1  |

|           | OP2 RIC          | CHARDsG | ]   | Item 11 of Active Record 2 |

|           | OP2 RI/<br>after | AsBCDEF | ]   | Item 11 of Active Record 2 |

|           | OP1 Asl<br>after | BCDEF   |     | Item 2 of Active Record 1  |

|           |                  |         |     |                            |

|           | No. 2            | 00      | 0P1 | 0P2                        |

|           |                  | 001     | 102 | 210                        |

|           | OP1 Asi          | BCDEF   |     | Item 2 of Active Record 2  |

|           | OP2 PQI          | RS      |     | Item 10 of Active Record 2 |

|           | OP2 CDI<br>after | EF      |     | Item 10 of Active Record 2 |

|           | OP1 Asi          | BCDEF   |     | Item 2 of Active Record 1  |

#### DATA MOVE

# //ove, Edit //nemonic Op Code = MED Octal Op Code = \*003

<u>PURPOSE</u>: To copy the data from one item right-aligned to another item under the control of a third mask item. Any remaining characters are replaced with the specified fill character.

| FORMAT: | 00  | 0P1  | 0P2  | 0P3  | 0P4 |

|---------|-----|------|------|------|-----|

|         | 003 | AR/I | AR/I | AR/I | L   |

<u>OPERATION</u>: A copy of the contents of the OP1 item is moved right-aligned into the OP3 item under control of the OP2 mask item. Every OP2 mask character that is equal to a null allows an OP1 item character to be moved into OP3. Every OP2 character that is not a null is itself moved to the OP3 item. After the move of all OP1 characters, leading zeros, spaces, commas, and nulls in the OP3 item are replaced by the fill literal specified in OP4. The low-order digit of the result has its four bits replaced with all ones (positive sign convention). The abnormal edit designator is set if the OP2 or OP3 item is smaller than the OP1 item.

| EXAMPLE: |               | OC OP1 ( | OP2 0P3          | 0P4                        |

|----------|---------------|----------|------------------|----------------------------|

|          |               | 003 101  | 102 212          | 134                        |

|          | OP1           | 00049984 | 2                | Item 1 of Active Record 1  |

|          | 0P2           | nnn,nnn, | nnn.nn           | Item 2 of Active Record 1  |

|          | OP3<br>before | <u> </u> | XX               | Item 12 of Active Record 2 |

|          | 0P4           | ★ Litera | al asterisk (134 | in EBCDIC)                 |

|          | OP3<br>after  | **4,998. | 4 2              | Item 12 of Active Record 2 |

#### DATA MOVE Move Item, Left-Align, Fill Mnemonic Op Code = MF Octal Op Code = 004

- <u>PURPOSE</u>: To copy the data from one item to another, with the contents of the receiving item left-aligned and any remaining characters replaced by a specified fill character.

- FORMAT:

OC

OP1

OP2

OP3

004

AR/I

AR/I

L

- <u>OPERATION</u>: A copy of the contents of the OP1 item is moved left-aligned into the OP2 item. If OP2 is larger than OP1, the remaining characters at the right are replaced by the OP3 character. If OP1 is larger than OP2, the extra OP1 characters at the right are truncated.

| EXAMPLE: |              | 00     | 0P1 | 0P2    | . OP3                |

|----------|--------------|--------|-----|--------|----------------------|

|          |              | 004    | 124 | 215    | 000                  |

|          | 0P1          | GHIJ   |     | Item 2 | 4 of Active Record 1 |

|          | 0P2          | *****  |     | Item 1 | 5 of Active Record 2 |

|          | OP2<br>after | GHIJnn |     | Item 1 | 5 of Active Record 2 |

|          | 0P1<br>after | GHIJ   |     | Item 2 | 4 of Active Record 1 |

#### DATA MOVE Nove Item, Right-Align, Fill Nnemonic Op Code = MRF Octal Op Code = 005

- <u>PURPOSE</u>: To copy the data from one item to another, with the contents of the receiving item right-aligned and any remaining characters replaced by a specified fill character.

- FORMAT:

OC

OP1

OP2

OP3

005

AR/I

AR/I

L

- <u>OPERATION</u>: A copy of the contents of the OP1 item is moved right-aligned into the OP2 item. If OP2 is larger than OP1, the remaining characters at the left are replaced by the OP3 character. If OP1 is larger than OP2, the extra OP1 characters at the left are truncated.

| EXAMPLE: |              | 0Ċ     | 0P1 | 0P2    | OP3                   |

|----------|--------------|--------|-----|--------|-----------------------|

|          |              | 005    | 125 | 215    | 133                   |

|          | OP1          | 4.50   |     | Item 2 | 25 of Active Record 1 |

|          | 0P2          | *****  |     | Item 1 | 5 of Active Record 2  |

|          | OP2<br>after | SS4.50 |     | Item 1 | 5 of Active Record 2  |

|          | OP1<br>after | 4.50   |     | Item 2 | 5 of Active Record 1  |

#### DATA MOVE Move Item, Left-Justify, Fill Mnemonic Op Code = MJ Octal Op Code = 006

- <u>PURPOSE</u>: To copy the data from one item to another, with the content of the receiving item left-justified and any remaining characters replaced by a specified fill character.

- FORMAT:OCOP1OP2OP3006AR/IAR/IL

- <u>OPERATION</u>: A copy of the contents of the OP1 item is moved into the OP2 item and left-justified. Left-justification means that the leading (leftmost) nulls, spaces, and zeros in the OP1 item are *not* moved to the OP2 item and the remaining characters are left-aligned. Any remaining characters at the right of OP2 are replaced by the OP3 character. If OP1 is larger than OP2, the extra characters at the right are truncated.

| EXAMPLE: |              | OC 0P1            | OP2     | 0P3                |

|----------|--------------|-------------------|---------|--------------------|

|          |              | 006 117           | 212     | 116                |

|          | 0P1          | sznnAsBCn         | Item 17 | of Active Record 1 |

|          | 0P2          | 123456789123      | Item 12 | of Active Record 2 |

|          | OP2<br>after | AsBCn++++++       | Item 12 | of Active Record 2 |

|          | 0P1<br>after | <b>sznn</b> AsBCn | Item 17 | of Active Record 1 |

DATA MOYE Move Item, Right Justify, Fill Mnemonic Op Code = MRJ Octal Op Code = 007

<u>PURPOSE</u>: To copy the data from one item to another, with the content of the receiving item right-justified and any remaining characters replaced by a specified fill character.

| FORMAT: | 00  | 0P1 · | - OP2 | 0P3 |  |

|---------|-----|-------|-------|-----|--|

|         | 007 | AR/ I | AR/I  | L   |  |

<u>OPERATION</u>: A copy of the contents of the OP1 item is moved into the OP2 item and right-justified. Right-justification means that the trailing (rightmost) nulls and spaces in the OP1 item are *not* moved to the OP2 item and the remaining characters are right-aligned. Any remaining characters at the left of OP2 are replaced by the OP3 character. If OP1 is larger than OP2, the extra characters at the right are truncated.

| EXAMPLE: |              |    | 0C           | 0P1  |      | 0P2  |      | 0P3    |        |        |   |

|----------|--------------|----|--------------|------|------|------|------|--------|--------|--------|---|

|          |              |    | 007          | 120  |      | 212  |      | 116    | ]      |        |   |

|          | 0P1          | ns | AB.Csz       | nns  |      | Item | 20   | of A   | ctive  | Record | 1 |

|          | 0P2          | 12 | 123456789123 |      | Item | 12   | of A | Active | Record | 2      |   |

|          | OP2<br>after | ++ | ++nsAB       | .Csz |      | Item | 12   | of A   | Ctive  | Record | 2 |

|          | OP1<br>after | ns | AB.Csz       | nns  |      | Item | 20   | of A   | lctive | Record | 1 |

# DATA MOVE Move, Pack Mnemonic Op Code = MPT Octal Op Code = \*050

<u>PURPOSE</u>: To extract the digit portions from a source item and pack them into a destination item, eliminating the sign zones of all source bytes except the rightmost. Any remaining destination item positions are filled with binary zeros.

| FORMAT: | 00  | 0P1  | 0P2  |

|---------|-----|------|------|

|         | 050 | AR/I | AR/I |

<u>OPERATION</u>: The decimal information contained in OP1 is moved into OP2. The sign zone changes place with the digit zone and the resultant byte is moved right-aligned into OP2. The following transfers move only the digit zone into OP2, thereby packing the digit zones of two source bytes into one destination byte. After the contents of OP1 are packed into OP2, any remaining OP2 bytes are filled with binary zeros.

| EXAMPLES: | 00  | 0P1 | OP2 |

|-----------|-----|-----|-----|

|           | 050 | 321 | 102 |

1 1

1000

Item 21 of Active Record 3

0

0P1

$$\begin{array}{c} + & 1 & + & 2 & + & 7 \\ \hline & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & &$$

1 1 1 1

0 0

#### DATA MOVE

# Move, Unpack Mnemonic Op Code = MUP Octal Op Code = \*052

<u>PURPOSE</u>: To unpack packed decimal information from a source item right-aligned into a destination item. Data is moved into the destination item in zoned form. Any remaining OP2 item positions are filled with binary zeros.

# FORMAT:OCOP1OP2052AR/IAR/I

<u>OPERATION</u>: The OP1 item contains packed decimal data. The numerics and the sign of the rightmost OP1 byte are stored into the rightmost OP2 byte after the sign zone and the digit zone have been switched around. For the second OP1 byte, the four zone bits are added to the four lower bits and stored into OP2. Then four zone bits are added to the remaining upper four bits and stored into OP2. In this way, each OP1 byte produces two OP2 bytes. After the contents of OP1 are unpacked into OP2, any remaining byte positions in OP2 are filled with binary zeros.

| E) | ( | ρ | M | IP | L | E | : |

|----|---|---|---|----|---|---|---|

|    |   |   |   |    |   |   |   |

| 00  | OP1 | 0P2 |

|-----|-----|-----|

| 052 | 301 | 314 |

|               | Item 1 of Active Record 3               |

|---------------|-----------------------------------------|

| 0P1           |                                         |

|               | fill 1 9 7 6 +                          |

|               | Item 14 of Active Record 3              |

| 0P2<br>before | 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 |

|               | Item 14 of Active Record 3              |

| 0P2           | 1 1 1 1 0 0 0 1 1 1 1 1 1 0 0 1 1 1 1 1 |

| after         | zone 1 zone 9 zone 7 + $6$              |

### DATA MOVE

### Translate Code

#### Mnemonic Op Code = TRL

#### Octal Op Code = 140

- <u>PURPOSE</u>: To convert characters from one code, such as EBCDIC, to another code, such as USASCII.

- FORMAT:

OC

OP1

OP2

OP3

140

AR/I

AR/I

AR/I

- <u>OPERATION</u>: Each character of the OP1 item is sequentially translated into its equivalent binary code from the table of character codes in OP2 and sequentially entered into the OP3 item. The example below illustrates the translation process.

| EXAMPLE: | 00  | 0P1 | 0P2 | 0P3 |  |

|----------|-----|-----|-----|-----|--|

|          | 140 | 110 | 201 | 322 |  |

Item 10 of Active Record 1 is translated into Item 22 of Active Record 3 by means of the conversion table in Item 1 of Active Record 2.

0P1 С.

0P2

$A_2 B_2 C_2 \ldots Z_2 \ldots$

The OP1 item contains the characters ACT in code 1.

The binary value for each OP1 character is added to the first location of OP2, giving the location of the equivalent character in binary of code 2, which is then transferred to OP3.

0P3

A<sub>2</sub> C<sub>2</sub> T<sub>2</sub> \*\*\*\*

The code 2 equivalent is left-aligned and any extra characters are unaffected.

# DATA MOVE Move Literal Mnemonic Op Code = ML Octal Op Code = 141

<u>PURPOSE</u>: To fill an item with a specified character.

| FORMAT: | 00  | 0P1  | 0P2 |

|---------|-----|------|-----|

|         | 141 | AR/I | L   |

OPERATION: The OP2 literal is entered into each position of the OP1 item.

| EXAMPLE: |              | 00           | 0P1 | 0P2  |                                 |                            |

|----------|--------------|--------------|-----|------|---------------------------------|----------------------------|

|          |              | 141          | 103 | 133  |                                 |                            |

|          | 0P1<br>0P2   | ABCDEF       |     | Item | 3 of Active Re                  | cord 1                     |

|          | OP1<br>after | \$\$\$\$\$\$ |     |      | 3 of Active Re<br>al Character: | ecord 1<br>EBCDIC 133 = \$ |

|          |              |              |     |      |                                 | (Soo Appondix C)           |

(See Appendix C)

#### PROGRAM STARTING ADDRESS (P-BIAS)

All addresses referenced in the "branch to" operands are *relative* to the first address of the program instructions. Core-memory assignments are made after the program is written and the starting address of the program is stored in the PCB. The relative address of each branching instruction is added to the program starting address (P-Bias) during instruction execution.

The Branching instructions include the following:

- No Operation (1-19)

- GOTO Greater Than (1-20)

- GOTO Less Than (1-21)

- GOTO Not Equal (1-22)

- GOTO Equal (1-23)

- GOTO Not Less Than (1-24)

- GOTO Not Greater Than (1-25)

- GOTO Unconditionally (1-26)

- GOTO On Designators (1-27)

- GOTO On Switches (1-28)

- GOTO Binary Greater Than (1-29)

- GOTO Binary Less Than (1-30)

- GOTO Binary Non-Zero (1-31)

- GOTO Binary Zero (1-32)

- GOTO Binary > Zero (1-33)

- GOTO Binary < Zero (1-34)

- GOTO Decimal Greater. Than (1-35)

- GOTO Decimal Less Than (1-36)

- GOTO Decimal Non-Zero (1-37)

- GOTO Decimal Zero (1-38)

- GOTO Decimal > Zero (1-39)

- GOTO Decimal < Zero (1-40)

- GOTO On Count (1-41)

- GOTO Table (1-42)

- GOTO Return (Branch) (1-44)

- GOTO Subroutine (Branch) (1-45)

1-18

# No Operation Mnemonic Op Code = NOP Octal Op Code = 020

PURPOSE: No operation. The instruction sequence is not changed.

| FORMAT: | 00  | Branch to |

|---------|-----|-----------|

|         | 020 | Address   |

<u>OPERATION</u>: When the instruction is executed, no change to indicator lights, designators, data, or instruction sequence is made.

This instruction may be used temporarily in a sequence of instructions, where it will have no effect. The actual op code may be changed later to 'G', 'GE', 'GNE', 'GLT', or 'GGT', so that subsequent execution of the instruction may actually cause a branch to the specified address.

# GOTO Greater Than Mnemonic Op Code = GGT Octal Op Code = 021

<u>PURPOSE</u>: To cause a branch from the instruction execution sequence when a "greater than" condition exists.

| FORMAT: | 00  | Branch to |  |

|---------|-----|-----------|--|

|         | 021 | Address   |  |

~~

<u>OPERATION</u>: When this instruction is executed and the GREATER THAN condition designator *is set and* the EQUAL condition designator *is not set*, the instruction execution sequence is transferred to the "branch to" address; otherwise, the execution sequence continues with the next instruction. The designators are set by the execution of other instructions.

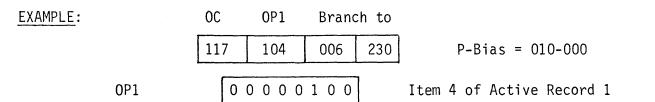

EXAMPLE:

| UL  | Branci | n to |

|-----|--------|------|

| 021 | 001    | 234  |

Design and the

P-Bias = 010-000

# GOTO Less Than Mnemonic Op Code = GLT Octal Op Code = 022

<u>PURPOSE</u>: To cause a branch from the instruction execution sequence when a "less than" condition exists.

- FORMAT: OC Branch to

022 Address

- <u>OPERATION</u>: When this instruction is executed and the GREATER THAN and the EQUAL condition designators are not set, the instruction execution sequence is transferred to the "branch to" address; otherwise, the execution sequence continues with the next instruction. The designators are set by the execution of other instructions.

EXAMPLE:

OC Branch to

P-Bias = 010-000

### GOTO Not Equal

### Mnemonic Op Code = GNE Octal Op Code = 023

- <u>PURPOSE</u>: To cause a branch from the instruction execution sequence when a "not equal" condition exists.

- FORMAT: OC Branch to

O23 Address

- <u>OPERATION</u>: When this instruction is executed and the EQUAL condition designator is not set, the instruction execution sequence is transferred to the "branch to" address; otherwise, the execution sequence continues with the next instruction. The designators are set by the execution of other instructions.

- EXAMPLE:

OC Branch to

| 023 | 001 | 234 |

|-----|-----|-----|

P-Bias = 010-000

### GOTO Equal Mnemonic Op Code = GE Octal Op Code = 024

- <u>PURPOSE</u>: To cause a branch from the instruction execution sequence when an "equal" condition exists.

- FORMAT: OC Branch to

O24 Address

- <u>OPERATION</u>: When this instruction is executed and the EQUAL designator *is set*, the instruction execution sequence is transferred to the "branch to" address; otherwise, the execution sequence continues with the next instruction. The designators are set by the execution of other instructions.

EXAMPLE:

OC Branch to

| 024 001 | 234 |

|---------|-----|

P-Bias = 010-000

# GOTO Not Less Than Mnemonic Op Code = GNL Octal Op Code = 025

To cause a branch from the instruction execution sequence when a "not **PURPOSE:** less than" condition exists.

| FORMAT: | 00  | Branch to |

|---------|-----|-----------|

|         | 025 | Address   |

OPERATION: When this instruction is executed and the EQUAL condition designator is set, or the EQUAL condition designator is not set and the GREATER THAN condition designator is set, the instruction execution sequence is transferred to the "branch to" address; otherwise, the execution sequence continues with the next instruction. The designators are set by the execution of other instructions.

234

EXAMPLE:

0C Branch to 001

025

P-Bias = 010-000

# GOTO Not Greater Than Mnemonic Op Code = GNG Octal Op Code = 026

<u>PURPOSE</u>: To cause a branch from the instruction execution sequence when a "not greater than" condition exists.

| FORMAT: | 00  | Branch to |

|---------|-----|-----------|

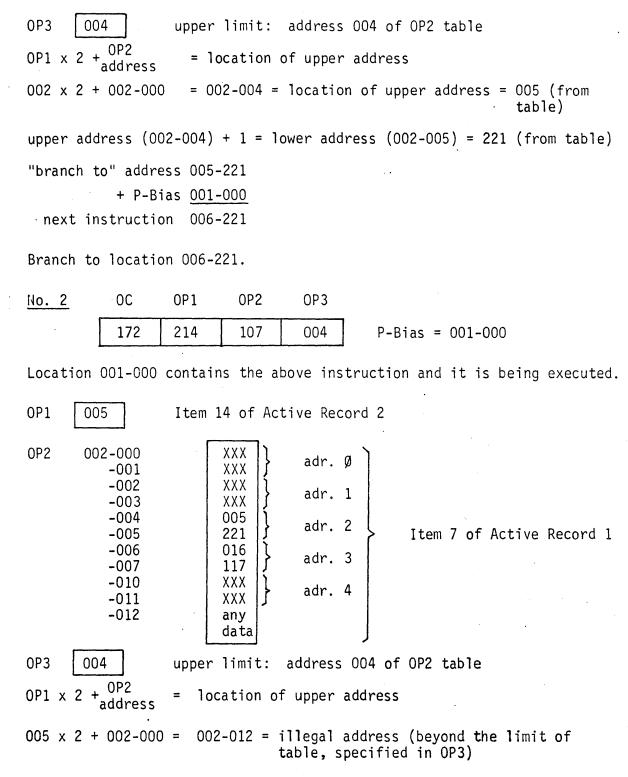

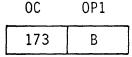

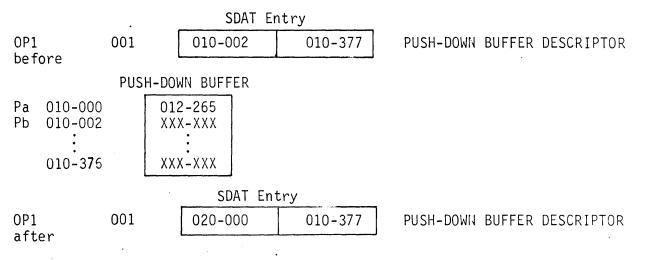

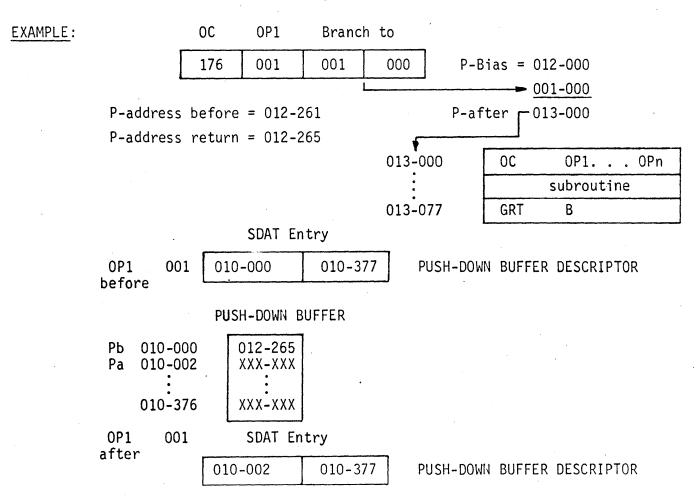

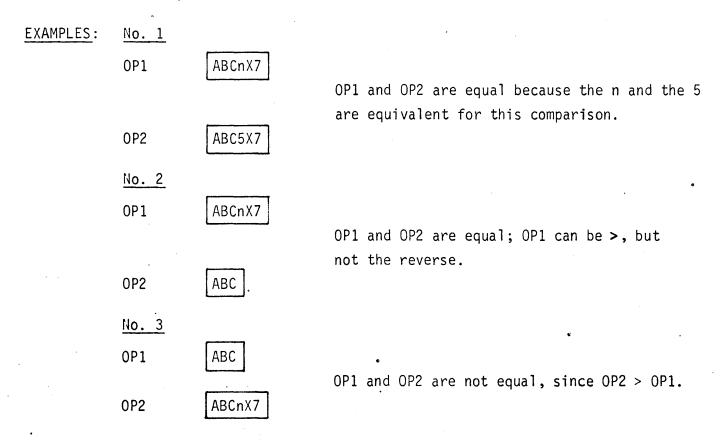

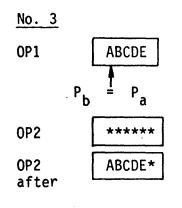

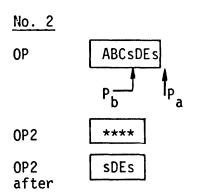

|         | 026 | Address   |